출처

tWCL=tWL=tCWL

tWCL=tWL=tCWL : 열린 메모리 뱅크(행, 열과 함께 메모리의 주소를 정의하는 단위)에 쓰는 데 걸리는 시간입니다. (메모리컨트롤러가 접근하고자 하는 셀이 운 좋게도 이미 열려있는 행 안에 있다면 앞서 행을 열기까지 수행한 tRP, tRCD를 생략할 수 있습니다.)

안정화에 있어서 필요한 타이밍이며. 낮은 값에 더 성능이 좋지만 일정 한계 값까지 내려 갈 경우 오히려 성능이 악화 되거나 안정화에 있어서 실패 합니다. CL값과 똑같거나 -1 값을 주는게 표준 입니다. 예를들어 CL 값이 17이면 tWCL값은 16 혹은 17이 적당 하다고 볼 수 있습니다.

tFAW , tRRD

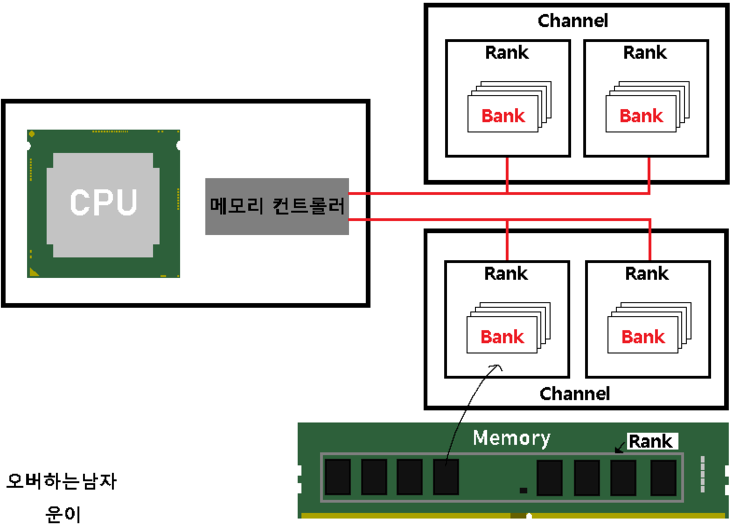

tFAW을 알아보기 위해선 램의 구조를 먼저 알아야 하니 밑 그림을 참고하면 좋습니다. (간략하게 그렸습니다.)

tFAW 는 정확히 4 개의 Active(ACT)=활성화 명령이 발행 된 후 새 메모리 뱅크가 활성화되기 전에 경과해야하는 시간입니다.

이게 무슨말이냐 하냐면,

메모리에 명령을 내릴땐 읽기,쓰기 동작을 하기 위해서는 BANK(행, 열과 함께 메모리의 주소를 정의하는 단위)를 활성화 해야 합니다. 여기서 세부램타중 하나인 tRRD와 밀접한 관련이 있습니다.

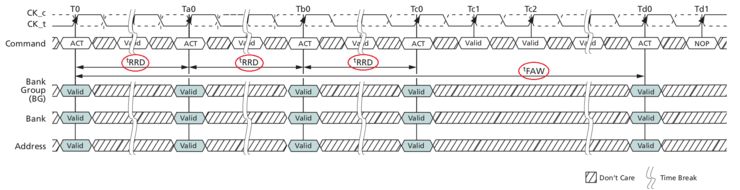

(그림출처 :https://www.systemverilog.io/understanding-ddr4-timing-parameters)

윗 그림 처럼 하나의 Bank를 Active(ACT)시켜주고 또 다른 Bank를 Active(ACT) 할 때는 tRRD만큼 간격을 꼭 주어야 합니다. 이처럼 tRRD는 한 Bank를 Active 시켜주고 또 다른 Bank를 Active할 때 그 행과 행의 간격 값이 tRRD 입니다. (두행 사이의 클록 수)

이때 Active 동작은 8BANK 메모리라 하더라도 tRRD간격으로 8BANK를 모두 연속으로 Active 할 수 없고, tFAW간격을 두고 최대 4개의 Bank만 Active할 수 있습니다. 그렇기에 tFAW은 쉽게말하면 4개의 뱅크가 얼마나 오랫동안 활성 상태를 유지할 수 있는지를 보여주는 시간 입니다.

성능값은 낮을 수록 좋지만 여기서 하나의 공식이 있습니다. 윗 사진을 봤듯이 절대로 tRRD값보다 tFAW값은 적어지면 안되며. 그렇기에 최소한 tRRD값의 x 4 (4개 뱅크 분할) 를 해줘야 하며 혹은 안정성을 원한다면 tRRD값의 x8을 해줘도 괜찮습니다. (램슬롯이 2개라 x2설정 하시는 분들도 계실텐데 아닙니다 그 물리적 bank와는 개념이 틀립니다.)

예를들어 tRRD값이 9일 경우 tFAW값은 36혹은 72가 나올 수 있다는 얘기 입니다. (값은 낮을 수록 성능이 좋습니다.)

-추가로 asus보드의 tRRD 부분의 tRRD_S(DRAM RAS# to RAS# Delay S) , tRRD_L(DRAM RAS# to RAS# Delay L) 차이는 S는 다른 Bank그룹 L은 동일한 Bank그룹 입니다. tRRD_S 값의 x4 해주시거나 x8 해주시면 됩니다.

램 오버는 값을 때려 넣는것 보다 그 값이 무엇을 의미 하는지를 잘 알아야 3박자가 고루 잘 갖춰 집니다.

간혹 램타를 보다가 의미없는 값을 줄이는 분들이 보이는데 .. 램타이밍을 A B C 로 나눠본다면

A가 치우 치거나 B,C가 치우 치거나 하면 안됍니다. ABC 서로의 합이 중요합니다.

A로 치우 쳤지만 안정화가 성공 한다면 실사하실 시에 시스템 불안 증세가 있을 겁니다. 부팅이 가끔 안된다던지. 밀린 다던지 등등이요.

특히 한쪽에 치우쳐진 상태에서 TRFC , TREFI 부분을 만질때 TREFI 값을 무작정 올리고 TRFC 타이트하게 꽉 조이다보면 어느새 보드와

cpu가 죽어있는 경험을 하실 수 있으니 조심하시길 바랍니다.

스크랩시 꼭 출처 부탁드립니다.

댓글 없음:

댓글 쓰기